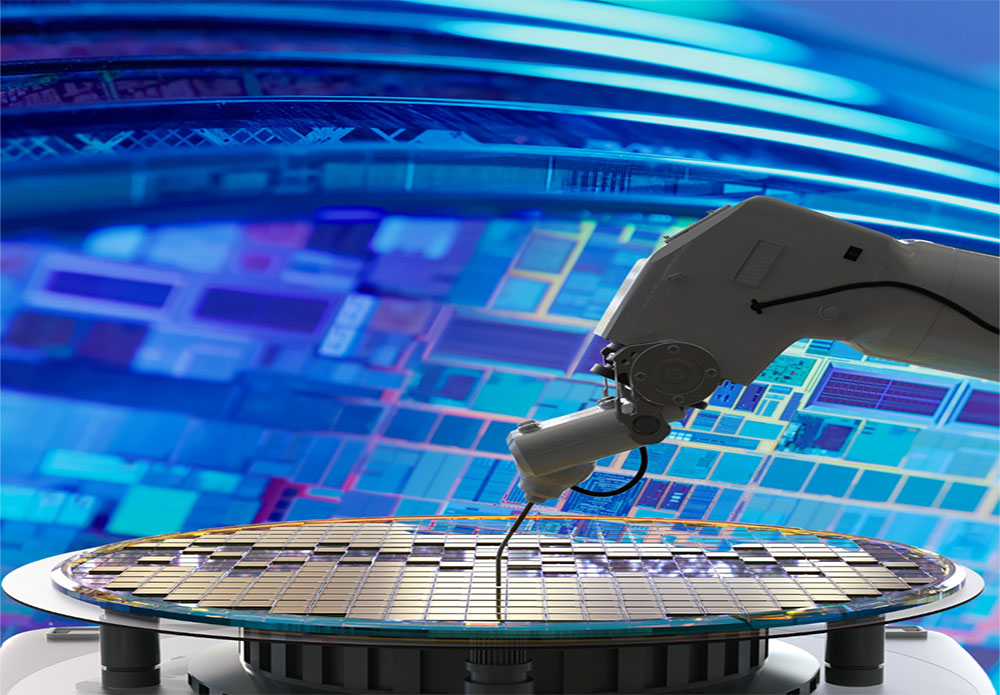

Design for Testability

A simple answer is DFT is a technique, which facilitates a design to become testable after production. It's the extra logic which we put in the normal design, during the design process, which helps its post-production testing. Post-production testing is necessary because, the process of manufacturing is not 100% error free.

Next Batch – TBD

Highly rated on Google

4.9/5

Course Duration

4 months

Learning Mode

Offline

Placement Assistance

100%

Career prospects in Design for Testability

The defects in silicon which contribute towards the errors introduced in the physical device. Of course a chip will not work as per the specifications if there are any errors introduced in the production process. But the question is how to detect that. Since, to run all the functional tests on each of say a million physical devices produced or manufactured, is very time consuming. This is where DFT engineers come into play.

Eligibility Criteria

B.TECH/B.E in Electrical Instrumentation

M.TECH in VLSI

B.Tech/B.E in Electronics and Communication(EEE)

B.Tech/B.E in Electrical and Electronics

Skills you will gain

Timing Closure

Static timing analysis

Debugging

ATPG

What you will learn

1. Basics of DLD

2. Overall VLSI flow

3. History, need and introduction to DFT

4. DFT Flow at high level

5. Hardware elements : PLL, Divider, Clock gater, Latch, TDR

6. Defect, Fault, Fault modelling & Error difference

7. Timing and its role in DFT

8. Basic UNIX commands

1. Intro : Basic flow and Architecture

2. Scan insertion types

- Internal scan

- Boundary scan

3. Scan methodology

4. Choosing parameters

5. Chain balancing

6. Library cells

7. Types of scanned Flip-flops

- MUX-D

- LSSD

1.Need for Compression

2.Compressor

3.Decompressor

- Ring oscillator

- Phase shifter

4.LFSR,LFSM

5.Compression ratio

6.Masking logic

7.Internal scan chains

8.Adding sub chains

9.Scan chain Re-order

10.EDT control signals

11.EDT clock and EDT update

12.EDT bypass logic

13.EDT lockup- latch/Terminal lockup-latch

14.Compression ratio

15.Faults inside EDT

1. What is ATPG?

2. Basic flow – inputs, process and outputs

3. Sequential depth

4. Fault models – Stuck, Transition and path delay

5. Fault identification/sensitization

6. Fault propagation and justification

7. Fault categories

8. Test procedures

9. LOS vs LOC

10. Coverage – Test and fault coverage

11. Coverage Debug

12. SDC in ATPG

13. Test time and test volume

14. Fault grading

15. SDC delivery for DFT modes

1.What is OCC?

- Advantages

- Disadvantages

- Internal structure of OCC

1. Simulations introduction and why we need

2. Simulation flow

3. Tools for simulation

4. Simulations types

- Serial simulations

- Parellel simulations

5. Scan simulation debugging

6. Chain simulation debugging

7. Timing & no timing simulations with differences?

8. Patten failure debugging with simulation and ATPG

1. Intro to MBIST

2. Intro to 1149.1 and TAP

3. Intro to Bscan

4. Intro to LBIST

5. Intro to diagnosis

6. Conclusion