IR

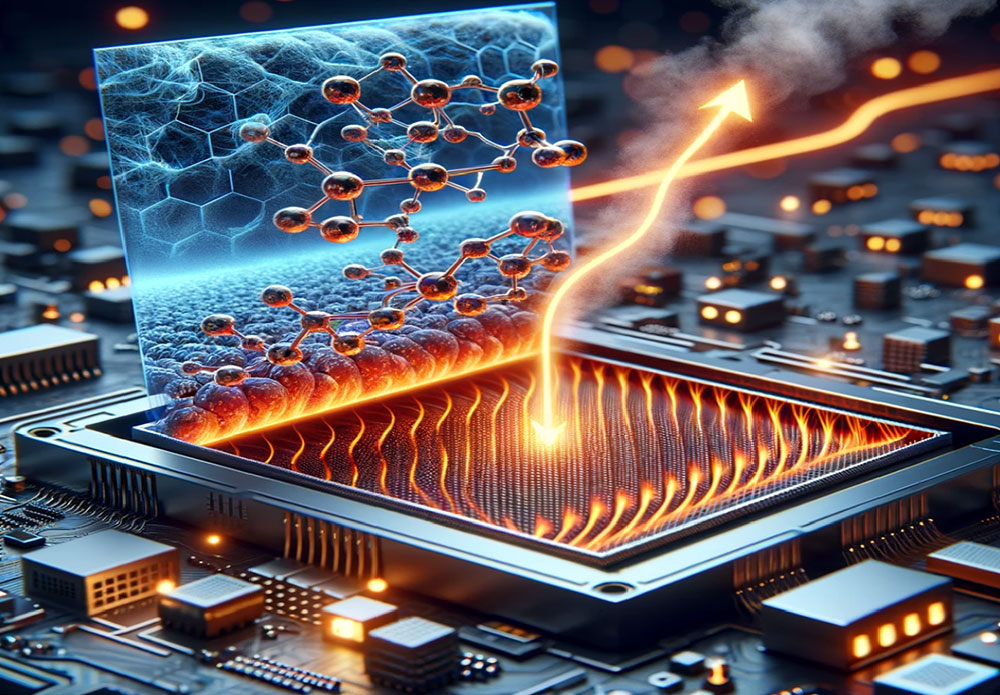

When a metal wire is subjected to a voltage, an electric current begins to pass through it. This flow of current encounters resistance within the wire, resulting in a reduction in voltage (as per Ohm's Law). This reduction is commonly referred to as IR drop. The process of examining the reasons behind this voltage drop and resolving any associated problems is known as IR drop analysis. The objective of this analysis is to ensure that all components in the design receive the necessary operating voltage. Additionally, it serves as one of the criteria for approving ASIC designs.

Next Batch – TBD

Highly rated on Google

4.9/5

Course Duration

4 months

Learning Mode

Offline

Placement Assistance

100%

Career prospects in IR

IR Engineer interact with the design team to solve the problems and also to propose new ideas,collaborate with the Design Automation team, to prototype, construct, modify and evaluate semiconductor devices and components.

Eligibility Criteria

B.TECH/B.E in Electrical Instrumentation

M.TECH in VLSI

B.Tech/B.E in Electronics and Communication(EEE)

B.Tech/B.E in Electrical and Electronics

Skills you will gain

RH Analysis Flow

RedHawk Tool

Reports Analysis

IR Issues

Low Power Design Analysis

What you will learn

1. Digital Basics

- Number System

- Boolean Algebra & Logic Gates

- Simplification of Boolean Functions using K-Maps

- Combinational Circuits

- Sequential Circuits

2. Networks Basics

- Charge, Current, Voltage, Energy, Power- Definitions and formulas

- R,L,C Basics, Series and Parallel Connections

- KVL and KCL

3. CMOS Basics

- Basic MOS and CMOS Structure and Related Parameteres

- PMOS and NMOS Basics-Operations,Regions, I-V characteristics

- CMOS Inverter Basics

- Stick Diagrams

- Latchup

1. Linux Basics

2. Vim / Gvim Basics

3. Scripting Language Basics(TCL/Python/PERL)

4. Asic Flow

1. Basics of IR Analysis

- What is IR drop analysis & Need for IR drop analysis

- Causes and Remedies for IR Drop

- Effects of IR Drop

- Average Power Formula

- Power grid Structure from source to follow Pin (Pmic(Power Management IC) to Gate )

- STA basics – Setup and Hold

2. Grid Check

- Introduction

- Inputs

- Command File

- Reports

- Issues

- Fixes

3. Static IR Analysis

- Introduction

- Inputs

- Command file

- Reports

- Issues

- Fixes

4. Dynamic IR Analysis

- Vless based Dynamic IR Analysis

- Introduction

- Inputs

- Command file

- Reports

- Issues

- Fixes

- VCD based Dynamic IR Analysis

- Introduction

- Inputs

- Command file

- Reports

- Issues

- Fixes

5. ElectroMigration (EM) Analysis-> Power&Signal

- Introduction

- Inputs

- Command file

- Reports

- Issues

- Fixes

6. ESD (Electrostatic Discharge)->B2B & C2I

- Introduction

- Inputs

- Command file

- Reports

- Issues

- Fixes

7. Low Power Design Analysis

- Introduction

- Inputs

- Low Power Design Techniques

- Low Power Cells

- Different Switch Operating States

- Switch Connectivity Pattern

- Power Gating Results

8. Ansys Apache RedHawk Tool Basics

- RH GUI Overview

- RH Tool Commands

9. HM level and Soc level Pro’s and Con’s

10. Block Explanation, Macros placed, congesions, Issues

11. RedHawk Analysis Fusion Tool inbuilt in Fusion Compiler